# 16-bit Proprietary Microcontroller

CMOS

# F<sup>2</sup>MC-16LX MB90520A/520B Series

# MB90522A/523A/522B/523B/F523B/V520A

### DESCRIPTION

The MB90520A/520B series is a general-purpose 16-bit microcontroller designed for process control applications in consumer products that require high-speed real-time processing.

The microcontroller instruction set is based on the AT architecture of the F<sup>2</sup>MC<sup>\*</sup> family with additional instructions for high-level languages, extended addressing modes, enhanced multiplication and division instructions, and a complete range of bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word (32-bit) data.

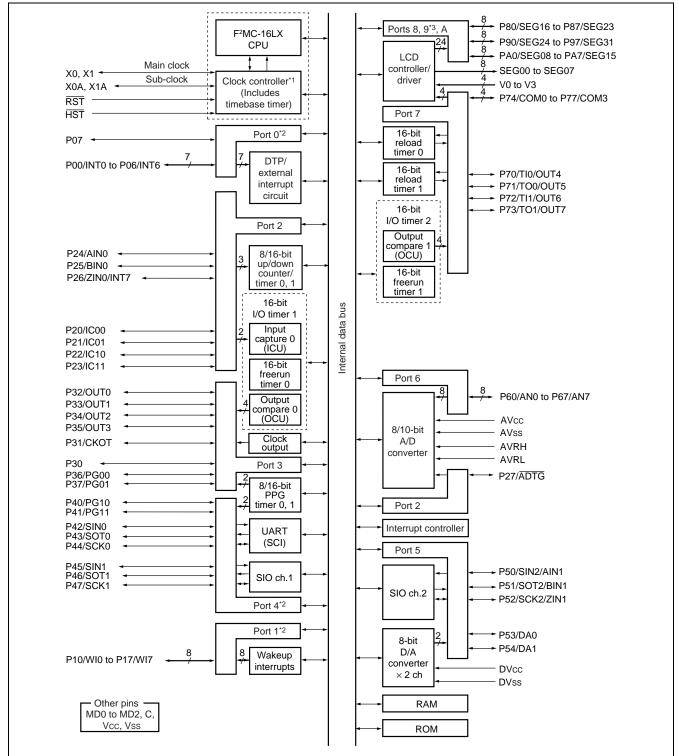

The MB90520A/520B series peripheral resources include an 8/10-bit A/D converter, 8-bit D/A converter, UART (SCI), extended I/O serial interfaces 0 and 1, 8/16-bit up/down counter/timers 0 and 1, 8/16-bit PPG timers 0 and 1, a range of I/O timers (16-bit free-run timers 1 and 2, input capture (ICU) 0 and 1, and output compare (OCU) 0 and 1), an LCD controller/driver, 8 external interrupt inputs, and 8 wakeup interrupts.

\*: F<sup>2</sup>MC stands for FUJITSU Flexible MicroController, a registered trademark of FUJITSU LIMITED.

#### ■ FEATURES

- Clock

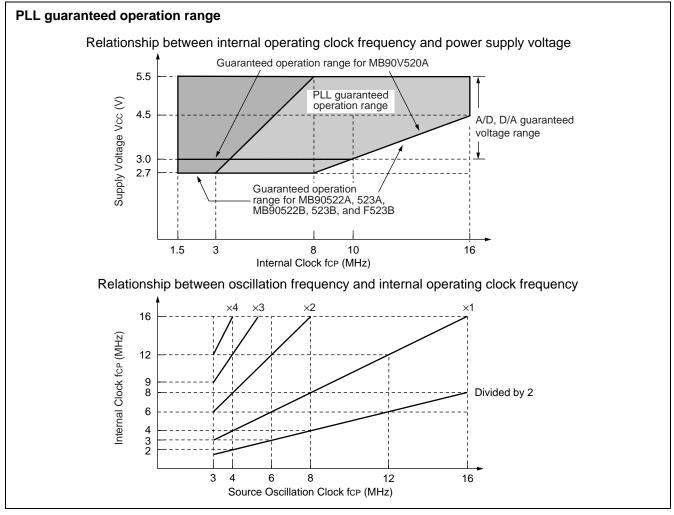

- Internal PLL clock multiplication circuit

- Selectable machine clock (PLL clock) : Base oscillation divided by two or multiplied by one to four (For a 4 MHz base oscillation, the machine clock range is 4 MHz to 16 MHz).

### PACKAGES

| (Continued)                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Sub-clock (32.768 KHz) operation available</li> </ul>                                                      |

| Minimum instruction execution time : 62.5 ns (for oscillation = 4 MHz, PLL clock setting = $\times$ 4, Vcc = 5.0 V) |

| <ul> <li>16MB CPU memory space</li> </ul>                                                                           |

| Internal 24-bit addressing                                                                                          |

| <ul> <li>Instruction set optimized for controller applications</li> </ul>                                           |

| Rich data types (bit, byte, word, long-word)                                                                        |

| Extended addressing modes (23 types)                                                                                |

| Enhanced signed multiplication and division instructions and RETI instruction                                       |

| Enhanced calculation precision using a 32-bit accumulator                                                           |

| <ul> <li>Instruction set designed for high-level language (C) and multi-tasking</li> </ul>                          |

| System stack pointer                                                                                                |

| Enhanced pointer-indirect instructions and barrel shift instructions                                                |

| Faster execution speed                                                                                              |

| 4-byte instruction queue                                                                                            |

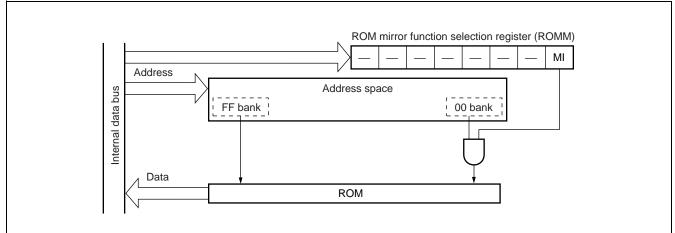

| ROM mirror function (48 Kbytes of bank FF is mirrored in bank 00)                                                   |

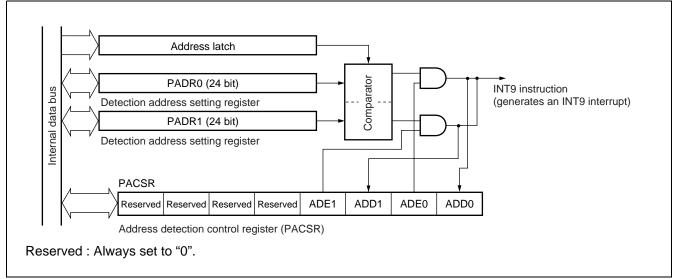

| <ul> <li>Program patch function : An address match detection function (2 × addresses)</li> </ul>                    |

| Interrupt function                                                                                                  |

| 32 programmable interrupts with 8 levels                                                                            |

| <ul> <li>Automatic data transmission function independent of CPU operation</li> </ul>                               |

| Extended intelligent I/O service function (EI2OS) : Up to 16 channels                                               |

| Low-power consumption (stand-by) modes                                                                              |

| Sleep mode (CPU operating clock stops, peripherals continue to operate.)                                            |

| Pseudo-clock mode (Only oscillation clock and timebase timer continue to operate.)                                  |

| Clock mode (Main oscillation clock stops, sub-clock and clock timer continue to operate.)                           |

| Stop mode (Main oscillation and sub-clock both stop.)                                                               |

| CPU intermittent operation mode                                                                                     |

| Hardware stand-by mode (Change to stop mpde by operating hardware stand-by pins.)                                   |

| Process                                                                                                             |

| CMOS technology                                                                                                     |

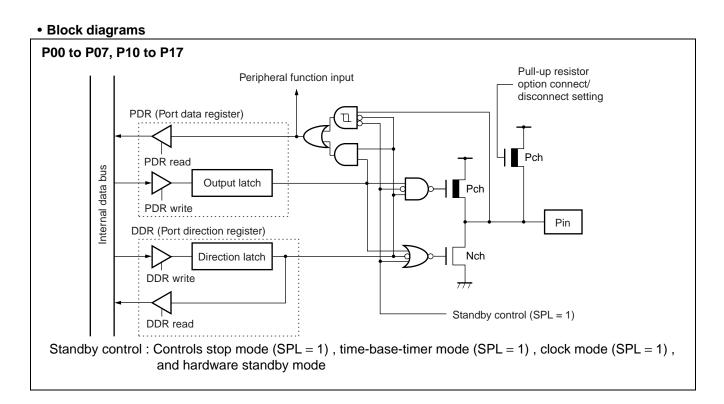

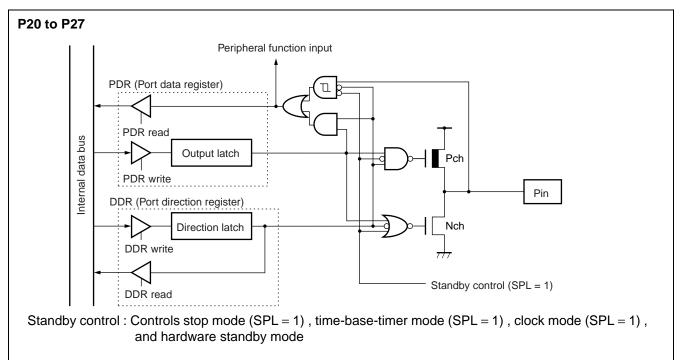

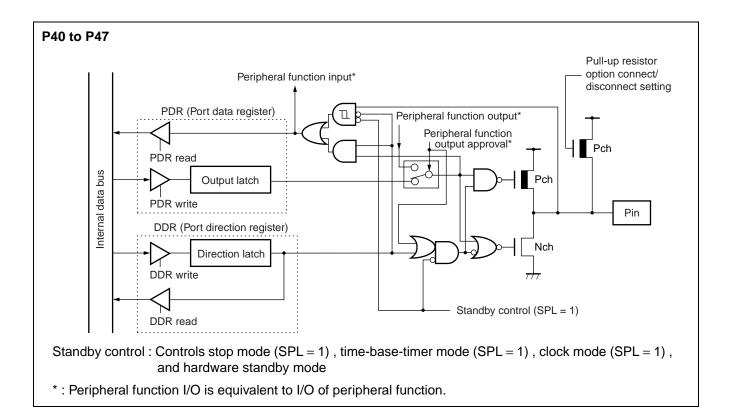

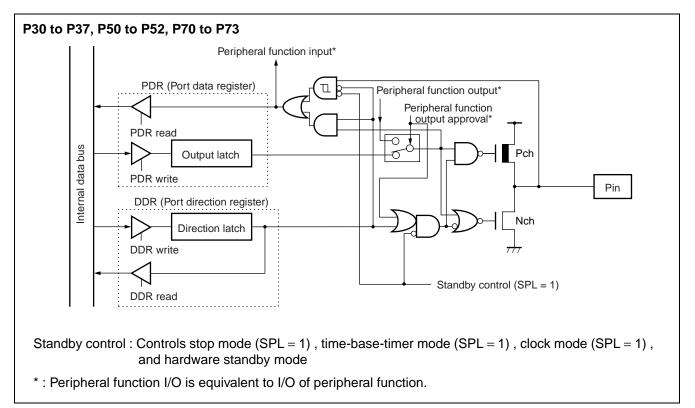

| I/O ports                                                                                                           |

| General-purpose I/O ports (CMOS input/output) : 53 ports                                                            |

| General-purpose I/O ports (inputs with pull-up resistors) : 24 ports                                                |

| General-purpose I/O ports (Nch open-drain outputs) : 8 ports                                                        |

| • Timers                                                                                                            |

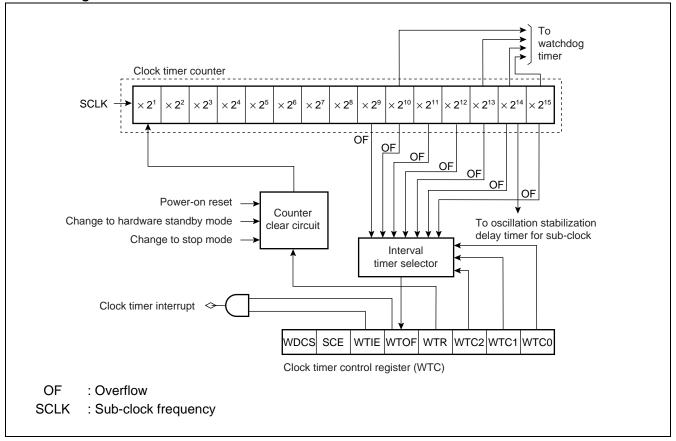

| Timebase timer, clock timer, watchdog timer : 1 channel each                                                        |

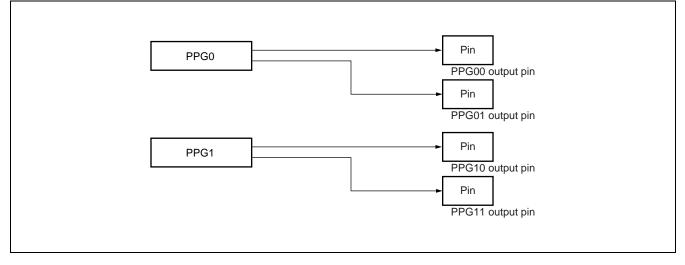

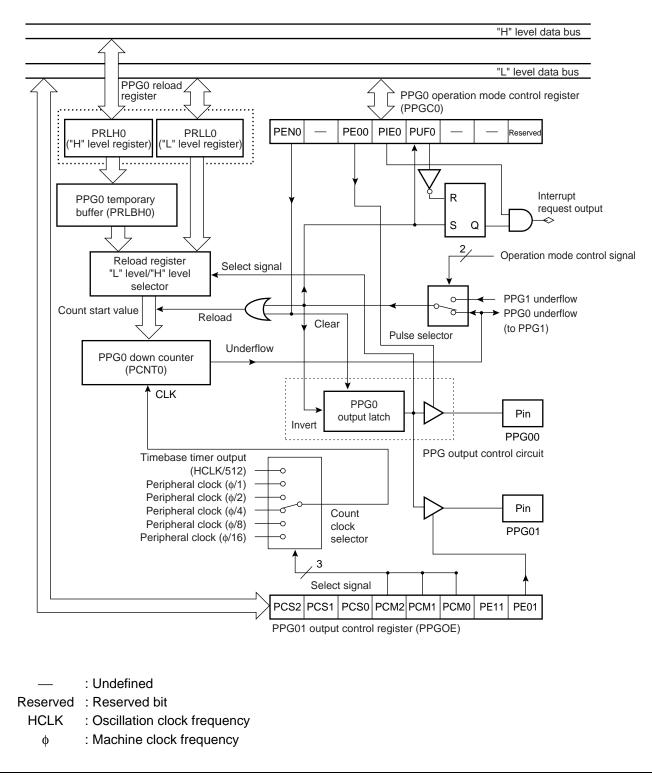

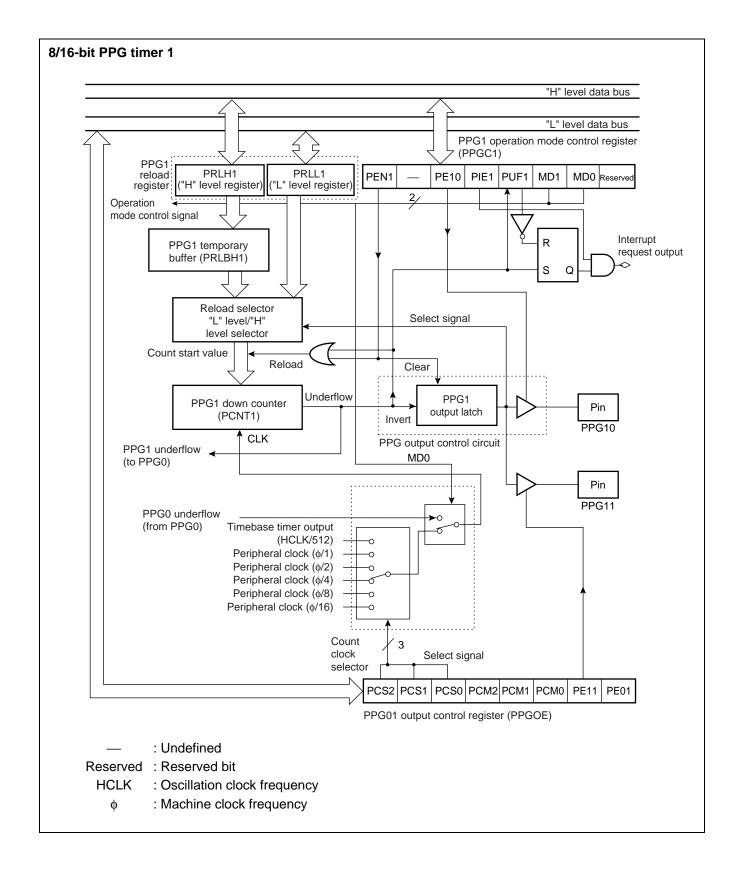

| 8/16-bit PPG timers 0 and 1 : 8-bit $	imes$ 2 channels or 16-bit $	imes$ 1 channel                                  |

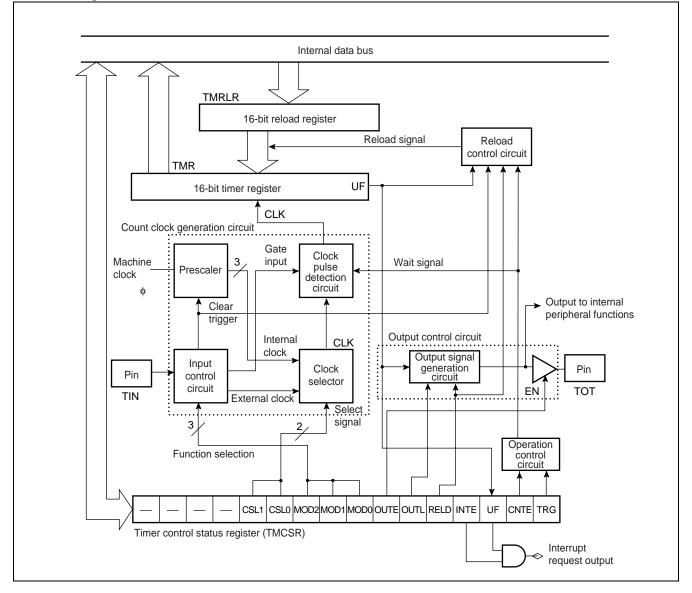

| 16-bit reload timers 0 and 1 : 2 channels                                                                           |

| 16-bit I/O timers :                                                                                                 |

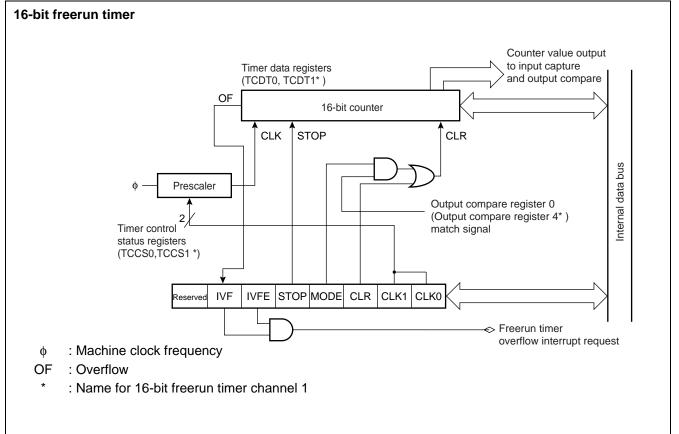

| 16-bit free-run timers 0 and 1 : 2 channels                                                                         |

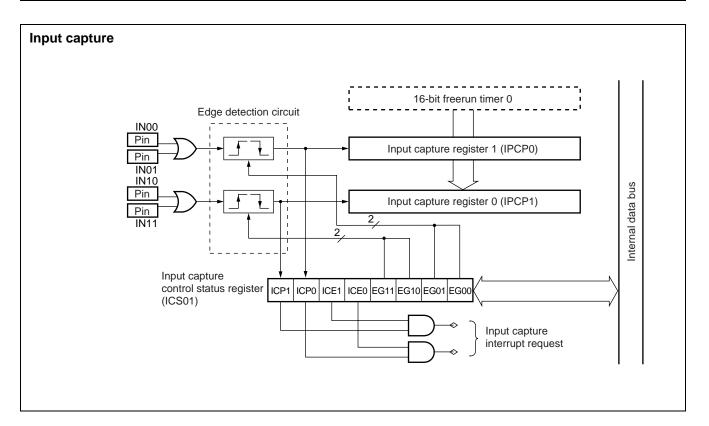

| 16-bit input capture 0 : 2 channels (2 channels per unit)                                                           |

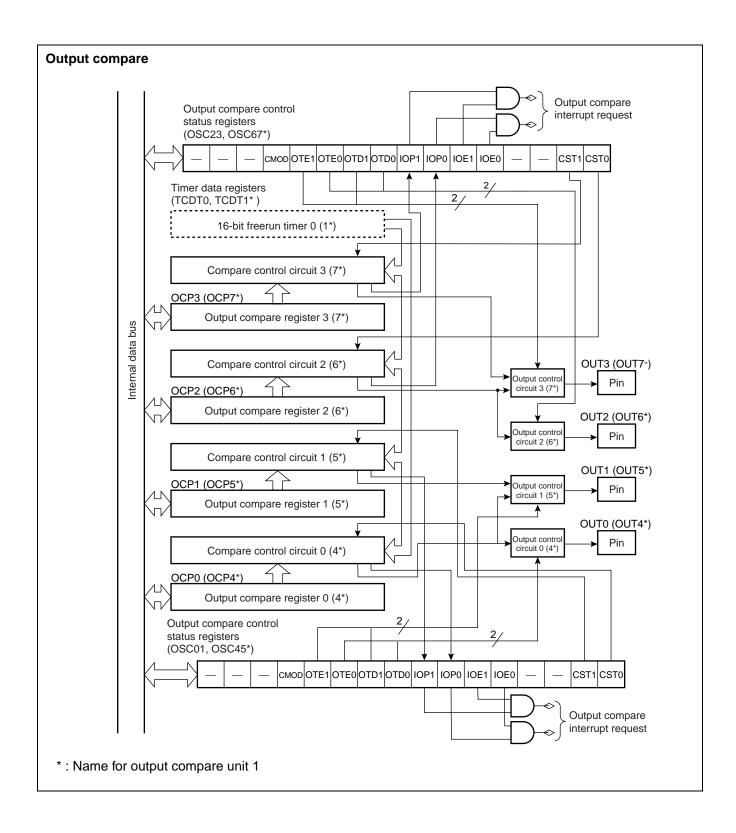

| 16-bit output compare 0 and 1 : 8 channels (4 channels per unit)                                                    |

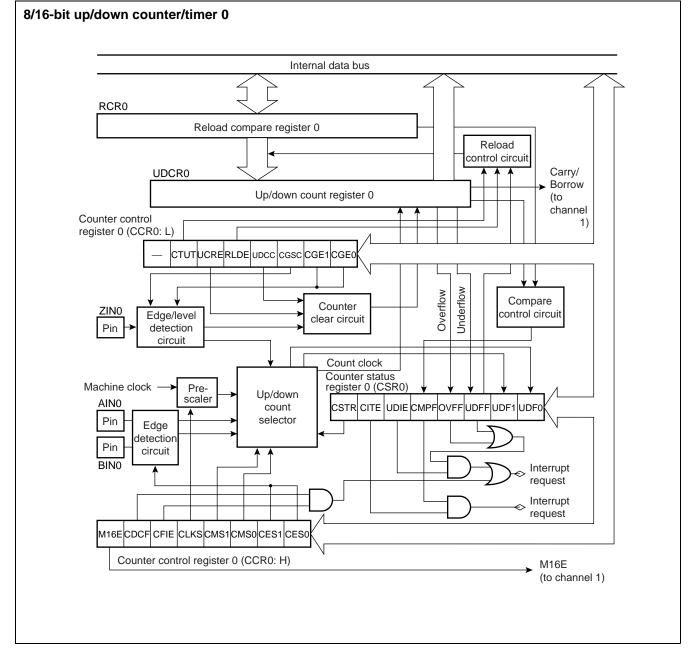

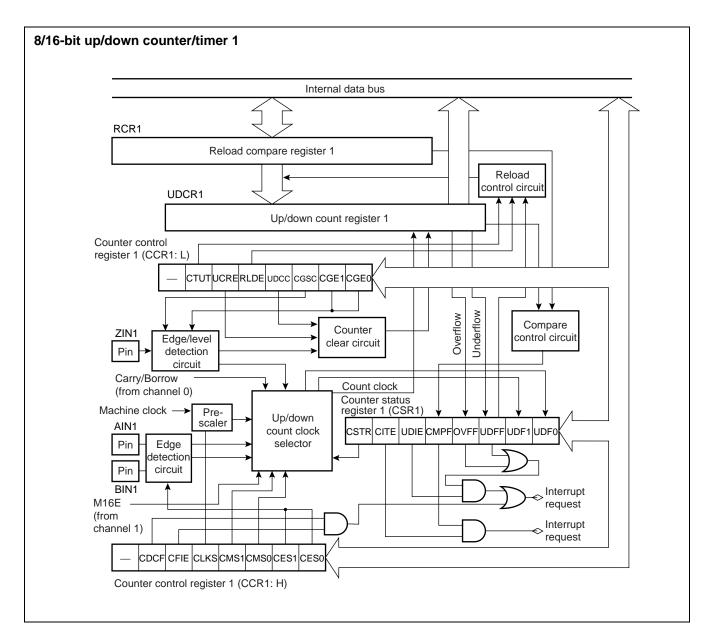

| 8/16-bit up/down counter/timers 0 and 1 : 8-bit $	imes$ 2 channels or 16-bit $	imes$ 1 channel                      |

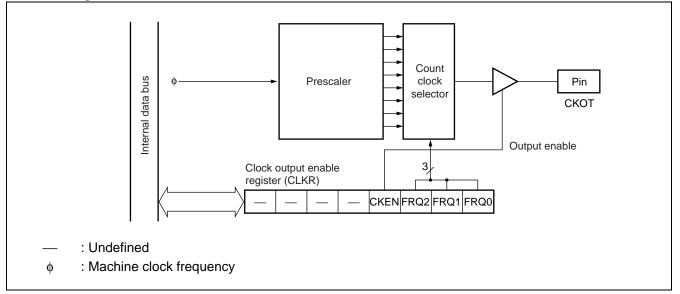

| Clock output function : 1 channel                                                                                   |

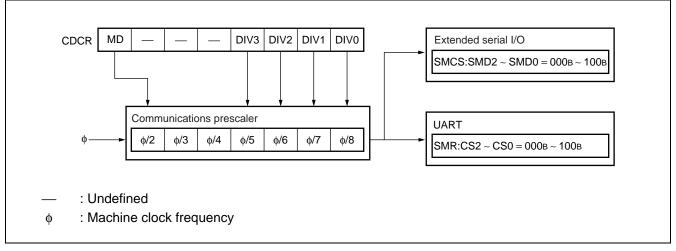

| <ul> <li>Communications macro (communication interface)</li> </ul>                                                  |

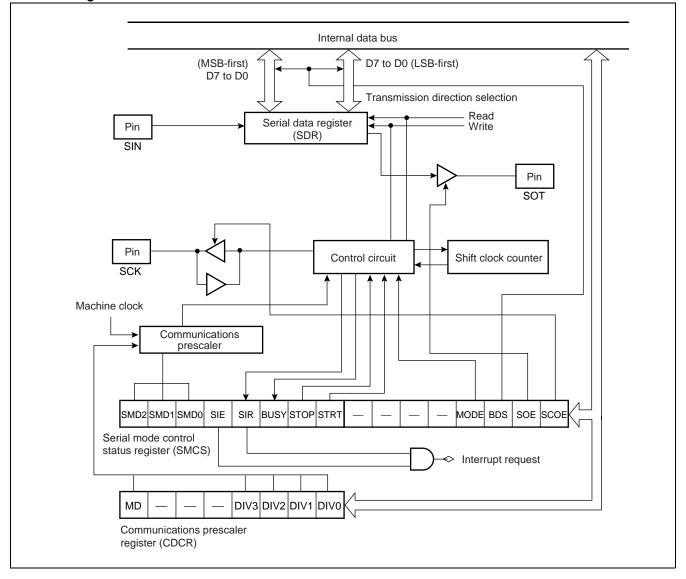

| Extended I/O serial interfaces 0 and 1 : 2 channels                                                                 |

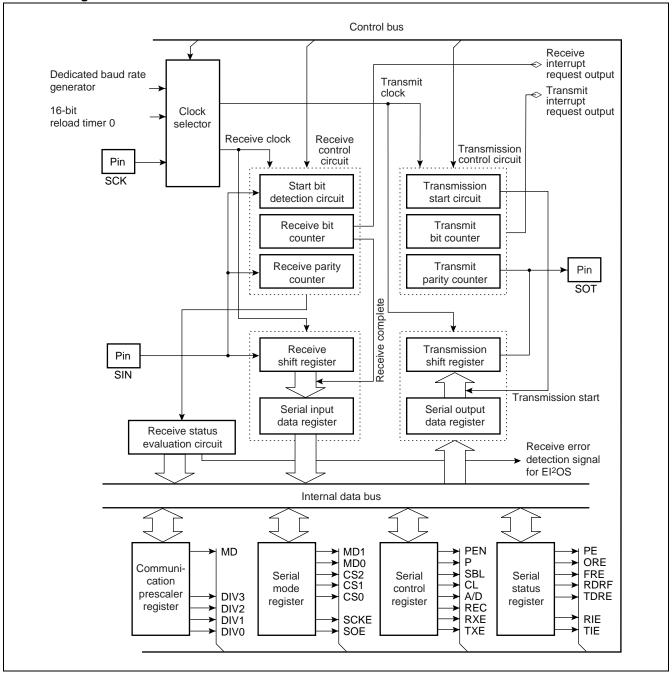

| UART (full-duplex, double-buffered, SCI : Can also be used for synchronous serial transfer) : 1 channel             |

|                                                                                                                     |

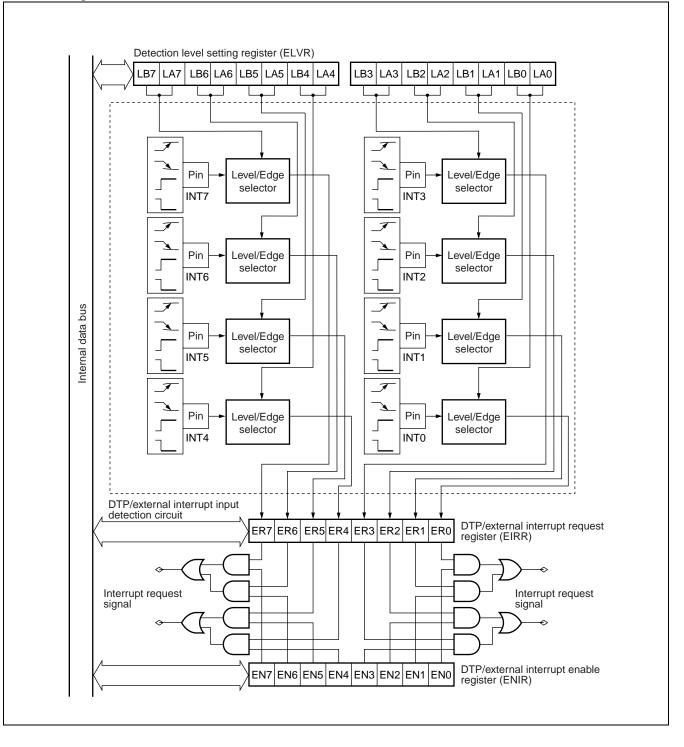

#### • External event interrupt control function

DTP/external interrupts : 8 channels (Can be set to detect rising edges, falling edges, "H" levels, or "L" levels) Wake-up interrupts : 8 channels (Detects "L" levels only) Delayed interrupt generation module : 1 channel (for task switching)

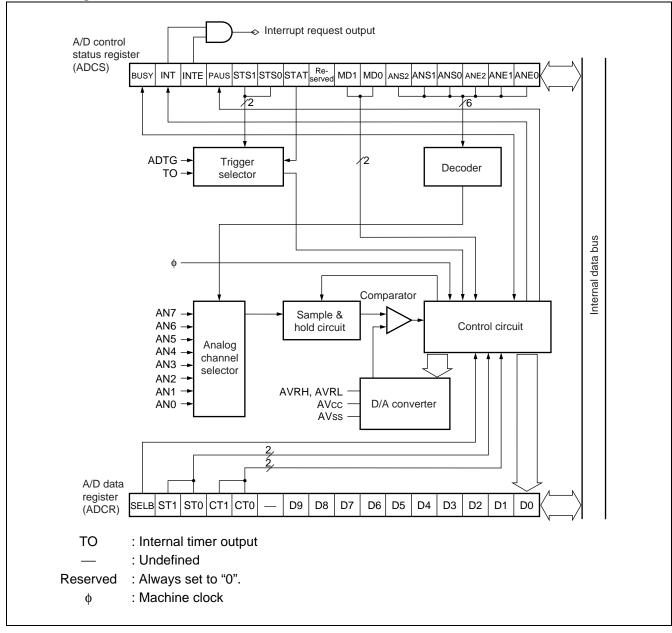

- Analog/digital conversion

8/10-bit A/D converter : 8 channels (Can be initiated by an external trigger. Minimum conversion time = 10.2 μs for a 16 MHz machine clock)

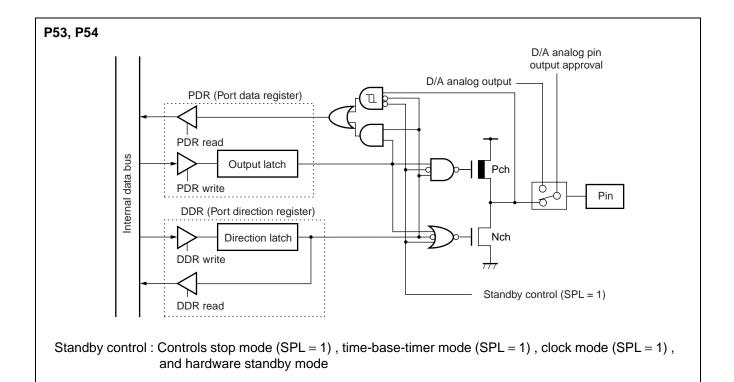

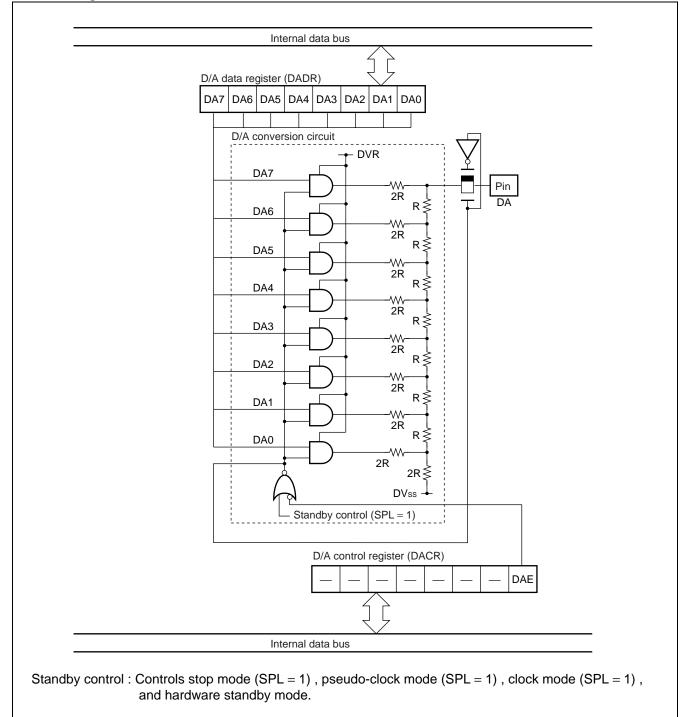

8-bit D/A converter : 2 channels (R-2R type. Settling time = 12.5 μs for a 16 MHz machine clock)

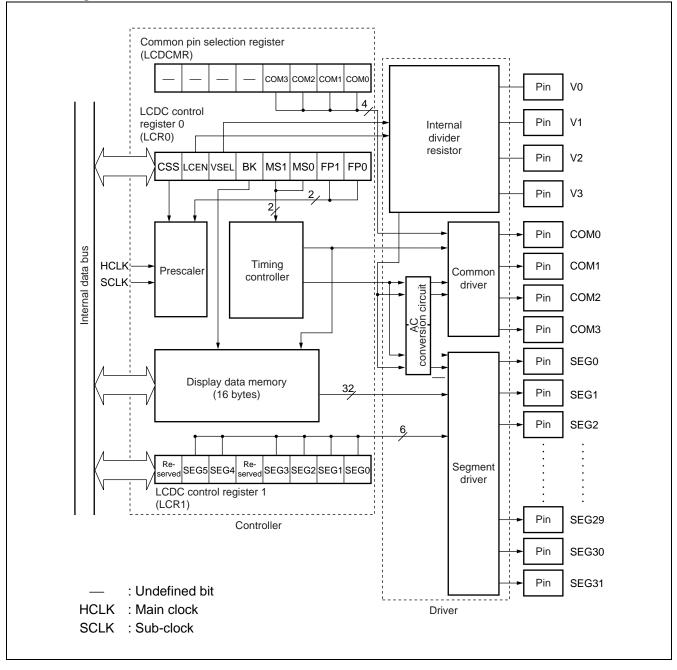

- Display function LCD controller/driver : 32 × segment drivers + 4 × common drivers

- Other

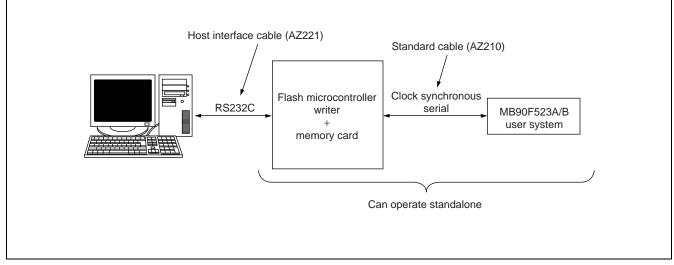

Supports serial writing to flash memory. (Only on versions with on-board flash memory.)

Note : The MB90520A and 520B series cannot be used in external bus mode. Always set these devices to singlechip mode.

### ■ PRODUCT LINEUP

| Parameter                   | Part<br>Number             | MB90522A                                                                                                                                                                                | MB90523A                                                                                                                                            | MB90522B      | MB90523B              | MB90F523B       | MB90V520A |  |  |

|-----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|-----------------|-----------|--|--|

| Classification              |                            |                                                                                                                                                                                         | Mask                                                                                                                                                | Flash ROM     | Evaluation<br>product |                 |           |  |  |

| ROM size                    |                            | 64 Kbytes                                                                                                                                                                               | 128 Kbytes                                                                                                                                          | 64 Kbytes     | 128 Kbytes            | 128 Kbytes      |           |  |  |

| RAM size                    |                            |                                                                                                                                                                                         |                                                                                                                                                     | 4 Kbytes      |                       |                 | 6 Kbytes  |  |  |

| Separate er<br>power supp   |                            |                                                                                                                                                                                         | _                                                                                                                                                   |               |                       |                 | No        |  |  |

| Process                     |                            |                                                                                                                                                                                         |                                                                                                                                                     | CM            | IOS                   |                 |           |  |  |

| Operating p<br>supply volta |                            | 3.0 V to                                                                                                                                                                                | o 5.5 V                                                                                                                                             | 2.7 V t       | o 5.5 V               | 3.0 V t         | o 5.5 V   |  |  |

| Internal reg                | ulator circuit             |                                                                                                                                                                                         | not mo                                                                                                                                              | ounted        |                       | mou             | inted     |  |  |

| CPU functio                 | ons                        | Instruction siz                                                                                                                                                                         | tructions : 340<br>es : 8-bit, 16-b<br>gth : 1 byte to<br>-bit, 8-bit, 16-b                                                                         | it<br>7 bytes |                       |                 |           |  |  |

|                             |                            | Minimum instr                                                                                                                                                                           | Minimum instruction execution time : 62.5 ns (for a 16 MHz machine clock)                                                                           |               |                       |                 |           |  |  |

|                             |                            | Interrupt processing time : 1.5 $\mu$ s min. (for a 16 MHz machine clock)                                                                                                               |                                                                                                                                                     |               |                       |                 |           |  |  |

| Low power<br>(standby m     |                            | Sleep mode, clock mode, pseudo-clock mode, stop mode, hardware standby mode, and CPU intermittent operation mode                                                                        |                                                                                                                                                     |               |                       |                 |           |  |  |

| I/O ports                   |                            | General-purpose I/O ports (CMOS outputs) : 53<br>General-purpose I/O ports (inputs with pull-up resistors) : 24<br>General-purpose I/O ports (Nch open drain outputs) : 8<br>Total : 85 |                                                                                                                                                     |               |                       |                 |           |  |  |

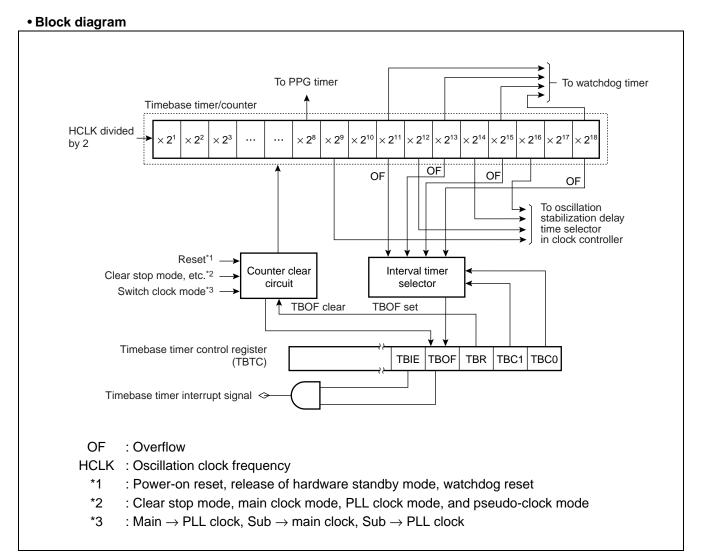

| Timebase ti                 | mer                        | 18-bit counter<br>Interrupt interval : 1.024 ms, 4.096 ms, 16.384 ms, 131.072 ms<br>(for a 4 MHz base oscillation)                                                                      |                                                                                                                                                     |               |                       |                 |           |  |  |

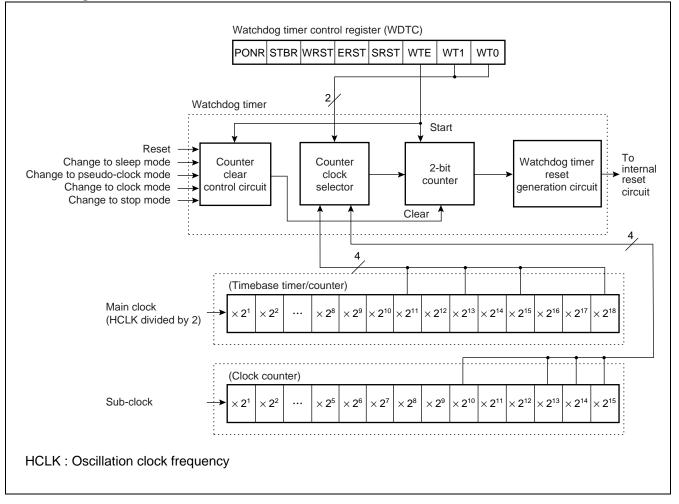

| Watchdog t                  | imer                       | Reset trigger period<br>• For a 4 MHz base oscillation : 3.58, 14.33, 57.23, 458.75 ms<br>• For 32.768 sub-clock operation : 0.438, 3.500, 7.000, 14.000 s                              |                                                                                                                                                     |               |                       |                 |           |  |  |

|                             | 16-bit<br>freerun<br>timer | Number of channels : 2<br>Generates an interrupt on overflow                                                                                                                            |                                                                                                                                                     |               |                       |                 |           |  |  |

|                             |                            | Number of channels : 8<br>Pin change timing : Free run timer register value equals output compare register value.                                                                       |                                                                                                                                                     |               |                       |                 |           |  |  |

|                             | 16-bit<br>input<br>capture | Number of channels: 2<br>Saves the value of the freerun timer register when a pin input occurs (rising edge, fa<br>edge, either edge).                                                  |                                                                                                                                                     |               |                       | g edge, falling |           |  |  |

| 16-bit reloa                | d timer                    | Count clock fr                                                                                                                                                                          | Number of channels : 2<br>Count clock frequency : 0.125, 0.5, or 2.0 μs for a 16 MHz machine clock<br>Can be used to count an external event clock. |               |                       |                 |           |  |  |

(Continued)

| (Continued) Part                                             |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 |                                              |                |                   |                |  |  |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------|----------------|-------------------|----------------|--|--|

| Number<br>Parameter                                          | MB90522A                                                                                                                                                                                                                                                                                                                                                                                  | MB90523A                                                                                        | MB90522B                                     | MB90523B       | MB90F523B         | MB90V520A      |  |  |

| Clock timer                                                  | 15-bit timer<br>Interrupt interv                                                                                                                                                                                                                                                                                                                                                          | 15-bit timer<br>Interrupt interval : 0.438, 0.5, or 2.0 μs for sub-clock frequency = 32.768 kHz |                                              |                |                   |                |  |  |

| 8/16-bit PPG timer                                           |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                 | t be used in 2 × borm output with            |                |                   | 0% duty ratio. |  |  |

| 8/16 -bit up/down<br>counter/timers                          | External event                                                                                                                                                                                                                                                                                                                                                                            | t inputs : 6 cha                                                                                | i be used in 2 ×<br>nnels<br>·bit × 2 channe |                | mode)             |                |  |  |

| Clock monitor                                                | Clock output f                                                                                                                                                                                                                                                                                                                                                                            | requency : Ma                                                                                   | chine clock/21 t                             | o machine cloo | ck/2 <sup>8</sup> |                |  |  |

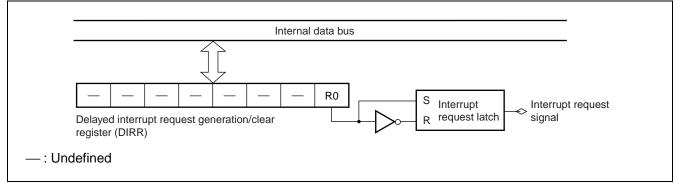

| Delayed interrupt generation module                          | Interrupt gene                                                                                                                                                                                                                                                                                                                                                                            | ration module                                                                                   | for task switchi                             | ng. (Used by I | REALOS.)          |                |  |  |

| DTP/External<br>interrupts                                   | Input channels : 8<br>Generates interrupts to the CPU on rising edges, falling edges with input "H" level, or "L"<br>level.<br>Can be used for external event interrupts and to activate El <sup>2</sup> OS.                                                                                                                                                                              |                                                                                                 |                                              |                |                   |                |  |  |

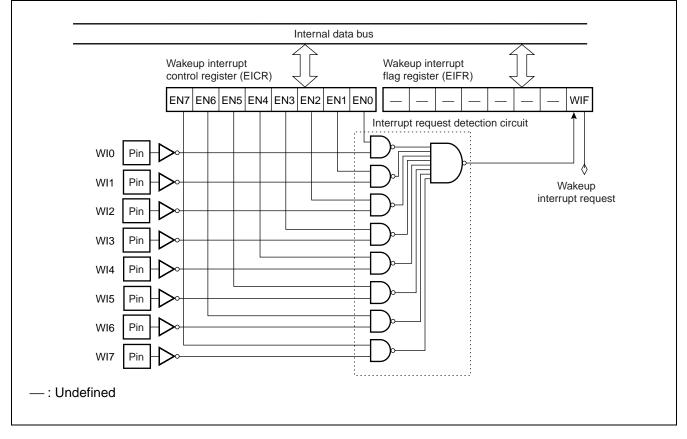

| Wakeup interrupts                                            | Input channels<br>Triggered by "                                                                                                                                                                                                                                                                                                                                                          |                                                                                                 |                                              |                |                   |                |  |  |

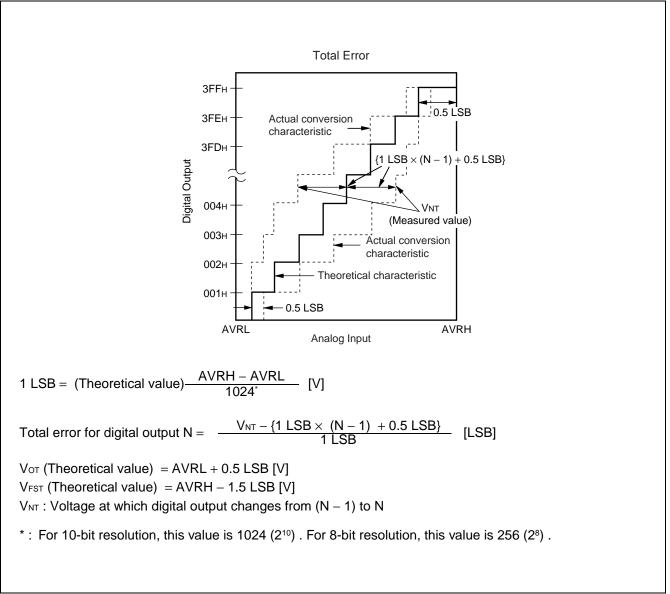

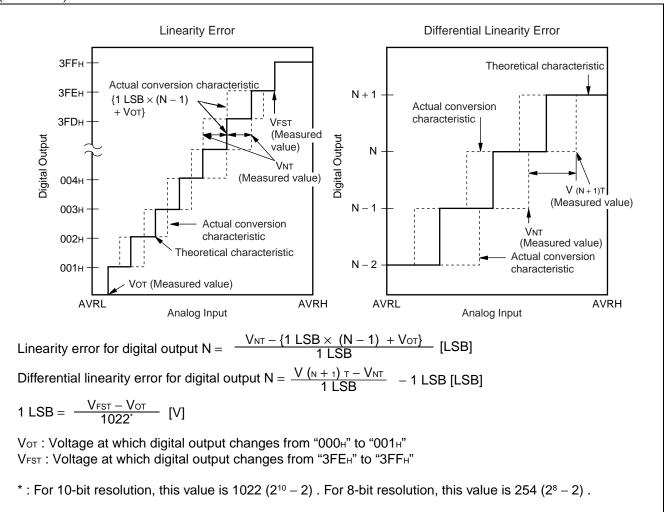

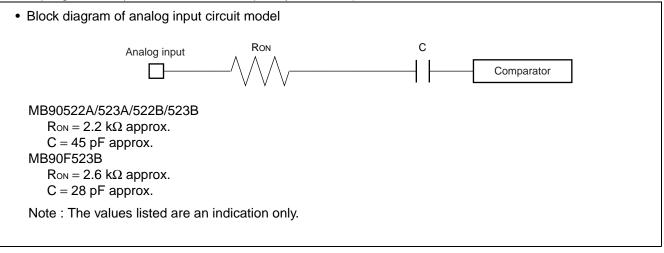

| 8/10-bit A/D converter<br>(successive<br>approximation type) | Number of channels : 8<br>Resolution : 8-bit or 10-bit selectable<br>Conversion can be performed sequentially for multiple consecutive channels.<br>• Single-shot conversion mode : Converts specified channel once only.<br>• Continuous conversion mode : Repeatedly converts specified channel.<br>• Intermittent conversion mode : Converts specified channel then halts temporarily. |                                                                                                 |                                              |                |                   |                |  |  |

| 8-bit D/A converter<br>(R-2R type)                           | Number of channels : 2<br>Resolution : 8-bit                                                                                                                                                                                                                                                                                                                                              |                                                                                                 |                                              |                |                   |                |  |  |

| UART (SCI)                                                   | Number of channels : 1<br>Clock synchronous transfer : 62.5 Kbps to 1 Mbps<br>Clock asynchronous transfer : 1202 bps to 31250 bps<br>Supports bi-directional and master-slave communications.                                                                                                                                                                                             |                                                                                                 |                                              |                |                   |                |  |  |

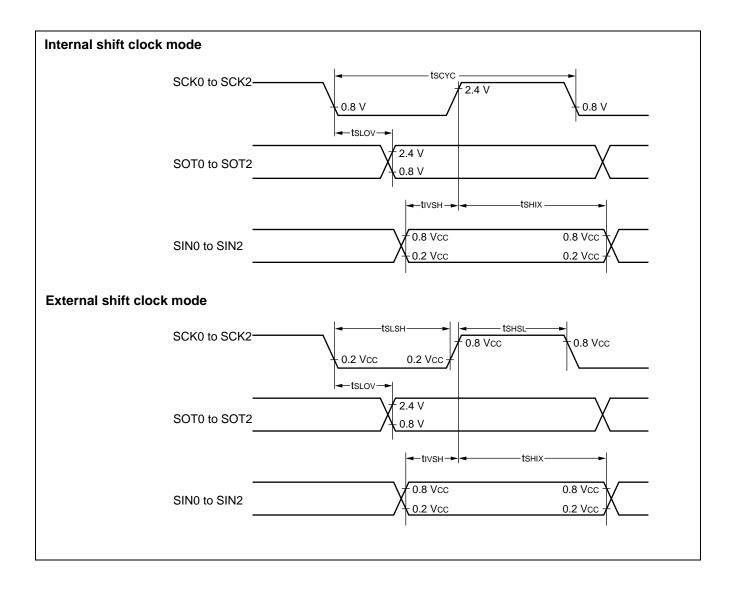

| Extended I/O serial interface                                | Number of channels : 2<br>Clock synchronous transfer : 31.25 Kbps to 1 Mbps (Using internal shift clock)<br>Transmission format : Selectable LSB-first or MSB-first                                                                                                                                                                                                                       |                                                                                                 |                                              |                |                   |                |  |  |

| LCD controller/driver                                        | Transmission format : Selectable LSB-first or MSB-first         Number of common outputs : 4         Number of segment outputs : 32         Number of power supply pins for LCD drive : 4         LCD display memory : 16 bytes         Divider resistor for LCD drive : Internal                                                                                                         |                                                                                                 |                                              |                |                   |                |  |  |

\*1 : As for the necessity of a DIP switch setting (S2) when using the emulation pod (MB2145-507) . Refer to the hardware manual for the emulation pod (MB2145-507) fomr details.

\*2 : Take note of the maximum operating frequency and A/D converter precision restrictions when operating at 3.0 V to 3.6 V. See the "Electrical Characteristics" section for details.

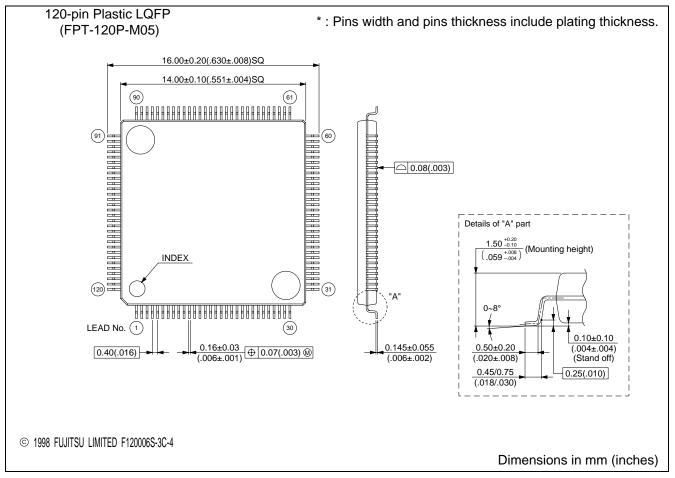

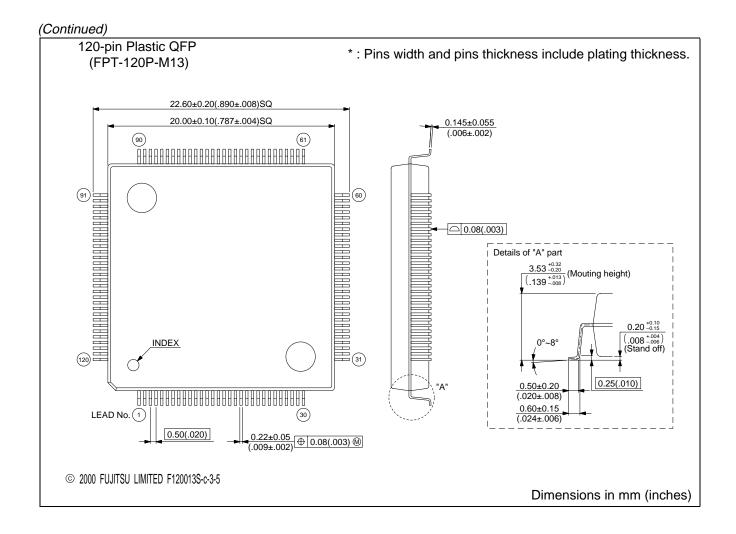

### ■ PACKAGES AND CORRESPONDING PRODUCTS

| Package                | MB90522A | MB90523A | MB90522B | MB90523B | MB90F523B | MB90V520A |

|------------------------|----------|----------|----------|----------|-----------|-----------|

| FPT-120P-M05<br>(LQFP) | 0        | 0        | 0        | 0        | 0         | ×         |

| FPT-120P-M13<br>(QFP)  | 0        | 0        | 0        | 0        | 0         | ×         |

| PGA-256C-A01<br>(PGA)  | ×        | ×        | ×        | ×        | ×         | 0         |

$\odot\,$  : Available,  $\,\times\,$  : Not available

Note : See the "■ PACKAGE DIMENSIONS" section for more details.

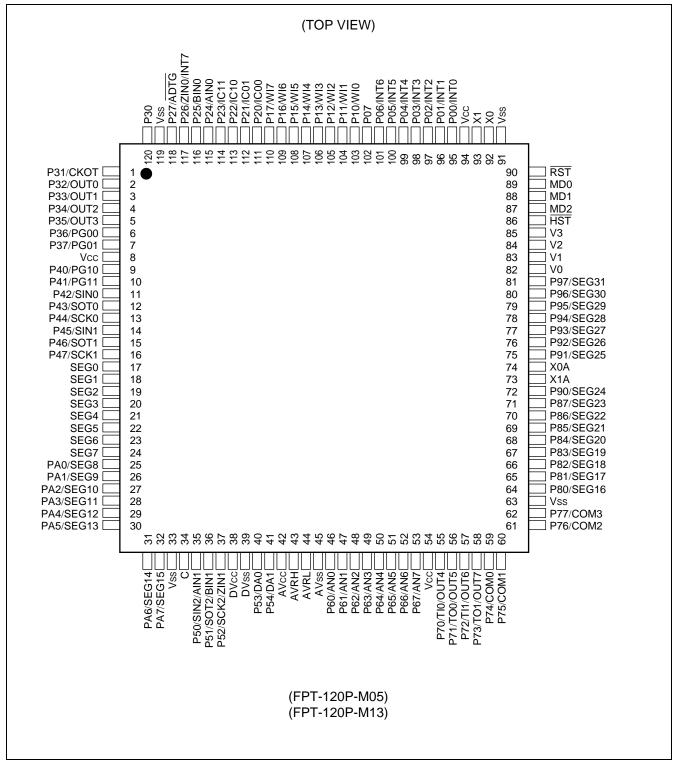

#### ■ PIN ASSIGNMENT

### ■ PIN DESCRIPTIONS

| Pin No.                                         |                           | Circuit         |                                                                                                                                                                                                                                                                                                       |  |

|-------------------------------------------------|---------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name                  | Circuit<br>Type | Function                                                                                                                                                                                                                                                                                              |  |

| 92, 93                                          | X0, X1                    | A               | Oscillator pin                                                                                                                                                                                                                                                                                        |  |

| 74, 73                                          | X0A, X1A                  | В               | Sub-oscillator pin                                                                                                                                                                                                                                                                                    |  |

| 89 to 87                                        | MD0 to<br>MD2             | С               | Input pins for setting the operation mode.<br>Connect directly to Vcc or Vss.                                                                                                                                                                                                                         |  |

| 90                                              | RST                       | С               | External reset input pin                                                                                                                                                                                                                                                                              |  |

| 86                                              | HST                       | С               | Hardware standby input pin                                                                                                                                                                                                                                                                            |  |

| 95 to 101                                       | P00 to<br>P06             | D               | General-purpose I/O ports<br>The settings in the pull-up resistor setup register (RDR0) are enabled<br>when ports are set as inputs.<br>The RDR0 settings are ignored when ports are set as outputs.                                                                                                  |  |

|                                                 | INT0 to<br>INT6           |                 | Event input pins for ch.0 to ch.6 of the DTP/external interrupt circuit                                                                                                                                                                                                                               |  |

| 102                                             | P07                       | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR0) are enabled when<br>ports are set as inputs.<br>The RDR0 settings are ignored when ports are set as outputs.                                                                                                   |  |

| 103 to 110                                      | P10 to<br>P17             | D               | General-purpose I/O ports<br>The settings in the pull-up resistor setup register (RDR1) are enabled when<br>ports are set as inputs.<br>The RDR1 settings are ignored when ports are set as outputs.                                                                                                  |  |

|                                                 | WI0 to<br>WI7             |                 | Event input pins for the wakeup interrupts.                                                                                                                                                                                                                                                           |  |

|                                                 | P20, P21,<br>P22, P23     |                 | General-purpose I/O ports                                                                                                                                                                                                                                                                             |  |

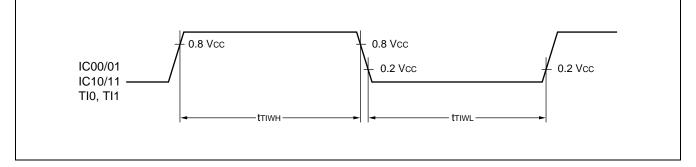

| 111, 112,<br>113, 114                           | IC00, IC01,<br>IC10, IC11 | E               | Trigger input pins for input capture units (ICU) 0 and 1.<br>Input operates continuously when channels 0 and 1 of input capture units<br>(ICU) 0 and 1 are operating. Accordingly, output to the pins from other func-<br>tions that share this pin must be suspended unless performed intentionally. |  |

|                                                 | P24                       |                 | General-purpose I/O port                                                                                                                                                                                                                                                                              |  |

| 115                                             | AIN0                      | E               | Also can be used as the count clock A input to 8/16-bit up/down counter/ timer 0.                                                                                                                                                                                                                     |  |

|                                                 | P25                       |                 | General-purpose I/O port                                                                                                                                                                                                                                                                              |  |

| 116                                             | BIN0                      | E               | Also can be used as the count clock B input to 8/16-bit up/down counter/ timer 0.                                                                                                                                                                                                                     |  |

|                                                 | P26                       |                 | General-purpose I/O port                                                                                                                                                                                                                                                                              |  |

| 117                                             | ZIN0                      | E               | Also can be used as the control clock Z input to 8/16-bit up/down counter/ timer 0.                                                                                                                                                                                                                   |  |

|                                                 | INT7                      |                 | Event input pin for ch.7 of the DTP/external interrupt circuit                                                                                                                                                                                                                                        |  |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

| Pin No.                                         |          | <b>O</b> imensit |                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name | Circuit<br>Type  | Function                                                                                                                                                                                                                                                                 |

|                                                 | P27      |                  | General-purpose I/O port                                                                                                                                                                                                                                                 |

| 118                                             | ADTG     | E                | External trigger input to the 8/10-bit A/D converter<br>Input operates continuously when the 8/10-bit A/D converter is performing<br>input. Accordingly, output to the pin from other functions that share this<br>pin must be suspended unless performed intentionally. |

| 120                                             | P30      | E                | General-purpose I/O port                                                                                                                                                                                                                                                 |

|                                                 | P31      |                  | General-purpose I/O port                                                                                                                                                                                                                                                 |

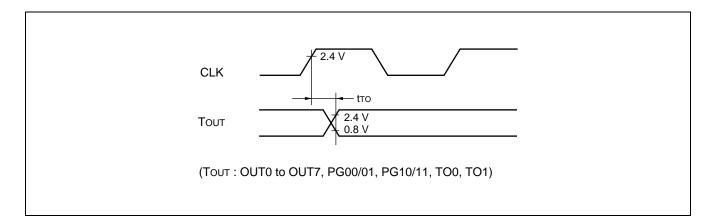

| 1                                               | СКОТ     | E                | Output pin for clock monitor function<br>The clock monitor is output when clock monitor output is enabled.                                                                                                                                                               |

| 2                                               | P32      | E                | General-purpose I/O port<br>Only available when waveform output from output compare 0 is disabled.                                                                                                                                                                       |

| 2                                               | OUT0     |                  | Event output pin for ch.0 of output compare unit 0 (OCU)<br>Only available when event output is enabled for output compare unit 0.                                                                                                                                       |

| 3                                               | P33      | E                | General-purpose I/O port<br>Only available when waveform output from output compare 1 is disabled.                                                                                                                                                                       |

| 3                                               | OUT1     |                  | Event output pin for ch.1 of output compare unit 0 (OCU)<br>Only available when event output is enabled for output compare unit 0.                                                                                                                                       |

| 4                                               | P34      | E                | General-purpose I/O port<br>Only available when waveform output from output compare 2 is disabled.                                                                                                                                                                       |

| 4                                               | OUT2     |                  | Event output pin for ch.2 of output compare unit 0 (OCU)<br>Only available when event output is enabled for output compare unit 0.                                                                                                                                       |

| 5                                               | P35      | E                | General-purpose I/O port<br>Only available when waveform output from output compare 3 is disabled.                                                                                                                                                                       |

| 5                                               | OUT3     |                  | Event output pin for ch.3 of output compare unit 0 (OCU)<br>Only available when event output is enabled for output compare unit 0.                                                                                                                                       |

| 6                                               | P36      | E                | General-purpose I/O port<br>Only available when waveform output from PG00 is disabled.                                                                                                                                                                                   |

| 0                                               | PG00     |                  | Output pin for 8/16-bit PPG timer 0<br>Only available when waveform output is enabled for PG00.                                                                                                                                                                          |

| 7                                               | P37      | E                | General-purpose I/O port<br>Only available when waveform output from PG01 is disabled.                                                                                                                                                                                   |

| 1                                               | 7 PG01   |                  | Output pin for 8/16-bit PPG timer 0<br>Only available when waveform output is enabled for PG01.                                                                                                                                                                          |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

| Pin No.                                         |               | 0::(            |                                                                                                                                                                                                                                                                               |

|-------------------------------------------------|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name      | Circuit<br>Type | Function                                                                                                                                                                                                                                                                      |

| 9, 10                                           | P40, P41      | D               | General-purpose I/O ports<br>Only available when waveform outputs from PG10 and PG11 are disabled.<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports are set as inputs. The RDR4 settings are ignored when ports<br>are set as outputs. |

|                                                 | PG10,<br>PG11 |                 | Output pins for 8/16-bit PPG timer 1<br>Only available when waveform output is enabled for PG10 and PG11.                                                                                                                                                                     |

| 11                                              | P42           | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports are set as inputs. The RDR4 settings are ignored when ports<br>are set as outputs.                                                                           |

|                                                 | SINO          | D               | UART (SCI) serial data input pin<br>Input operates continuously when the UART is performing input.<br>Accordingly, output to the pin from other functions that share this pin must<br>be suspended unless performed intentionally.                                            |

| 12                                              | P43           | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports are set as inputs. The RDR4 settings are ignored when ports<br>are set as outputs.                                                                           |

|                                                 | SOT0          |                 | UART (SCI) serial data output pin<br>Only available when serial data output is enabled for the UART (SCI).                                                                                                                                                                    |

| 13                                              | P44           | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports are set as inputs. The RDR4 settings are ignored when ports<br>are set as outputs.                                                                           |

|                                                 | SCK0          |                 | UART (SCI) serial clock input/output pin<br>Only available when serial clock output is enabled for the UART (SCI) .                                                                                                                                                           |

| 14                                              | P45           | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports set as inputs. The RDR4 settings are ignored when ports set<br>are as outputs.                                                                               |

| 14                                              | SIN1          | U               | Data input pin for extended I/O serial interface 1<br>Input operates continuously when the performing serial input. Accordingly,<br>output to the pin from other functions that share this pin must be<br>suspended unless performed intentionally.                           |

| 15                                              | P46           | D               | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports set as inputs. The RDR4 settings are ignored when ports are<br>set as outputs.                                                                               |

|                                                 | SOT1          |                 | Data output pin for extended I/O serial interface 1<br>Only available when serial data output is enabled for SOT1.                                                                                                                                                            |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

| Pin No.                                         | Pin No.       |                 |                                                                                                                                                                                                                                                                                |

|-------------------------------------------------|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name      | Circuit<br>Type | Function                                                                                                                                                                                                                                                                       |

| 16                                              | P47 D         |                 | General-purpose I/O port<br>The settings in the pull-up resistor setup register (RDR4) are enabled<br>when ports are set as inputs. The RDR4 settings are ignored when ports<br>are set as outputs.                                                                            |

|                                                 | SCK1          |                 | Serial clock input/output pin for extended I/O serial interface 1<br>Only available when serial clock output is enabled for SCK1.                                                                                                                                              |

|                                                 | P50           |                 | General-purpose I/O port                                                                                                                                                                                                                                                       |

| 35                                              | SIN2          | E               | Data input pin for extended I/O serial interface 2<br>Input operates continuously when the performing serial input.<br>Accordingly, output to the pin from other functions that share this pin must<br>be suspended unless performed intentionally.                            |

|                                                 | AIN1          |                 | Also can be used as the count clock A input to 8/16-bit up/down counter/ timer 1.                                                                                                                                                                                              |

|                                                 | P51           |                 | General-purpose I/O port                                                                                                                                                                                                                                                       |

| 36                                              | SOT2          | E               | Data output pin for extended I/O serial interface 2<br>Only available when serial data output is enabled for SOT2.                                                                                                                                                             |

|                                                 | BIN1          |                 | Also can be used as the count clock B input to 8/16-bit up/down counter/<br>timer 1.                                                                                                                                                                                           |

|                                                 | P52           |                 | General-purpose I/O port                                                                                                                                                                                                                                                       |

| 37                                              | SCK2          | E               | Serial clock input/output pin for extended I/O serial interface 2<br>Only available when serial clock output is enabled for SCK2.                                                                                                                                              |

|                                                 | ZIN1          |                 | Also can be used as the control clock Z input to 8/16-bit up/down counter/ timer 1.                                                                                                                                                                                            |

| 40 44                                           | P53, P54      |                 | General-purpose I/O ports                                                                                                                                                                                                                                                      |

| 40, 41                                          | DA0, DA1      |                 | Analog output pins for ch.0 and ch.1 of the 8-bit D/A converter                                                                                                                                                                                                                |

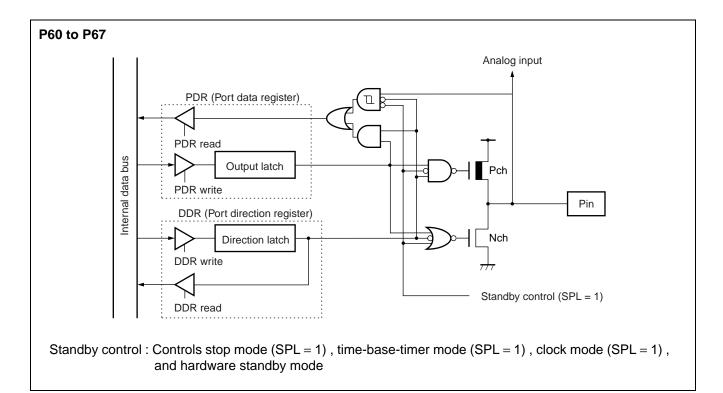

| 46 to 53                                        | P60 to P67    | К               | General-purpose I/O ports<br>Port input is enabled when the analog input enable register (ADER) is set<br>to the ports.                                                                                                                                                        |

| 40 10 55                                        | AN0 to<br>AN7 | , r             | Analog inputs for the 8/10-bit A/D converter<br>Analog input is enabled when the analog input enable register (ADER) is<br>set.                                                                                                                                                |

|                                                 | P70, P72      |                 | General-purpose I/O ports                                                                                                                                                                                                                                                      |

| 55, 57                                          | TIO, TI1      | E               | Event input pins for 16-bit reload timers 0 and 1<br>Input operates continuously when 16-bit reload timers 0 and 1 input an<br>external clock. Accordingly, output to these pins from other functions that<br>share the pins must be suspended unless performed intentionally. |

|                                                 | OUT4,<br>OUT6 |                 | Event output pins for ch. 4 and ch. 6 of output compare unit 1 (OCU)<br>Only available when event output from output compare 1 is enabled.                                                                                                                                     |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

| Pin No.                                         |                             | Circuit |                                                                                                                                                             |

|-------------------------------------------------|-----------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name                    | Туре    | Function                                                                                                                                                    |

|                                                 | P71, P73                    |         | General-purpose I/O ports<br>Only available when event outputs from 16-bit reload timers 0 and 1 are<br>disabled.                                           |

| 56, 58                                          | TO0, TO1                    | Е       | Output pins for 16-bit reload timers 0 and 1.<br>Only available when output is enabled for 16-bit reload timers 0 and 1.                                    |

|                                                 | OUT5,<br>OUT7               |         | Event output pins for ch. 5 and ch. 7 of output compare unit 1 (OCU)<br>Only available when event output from output compare 1 is enabled.                  |

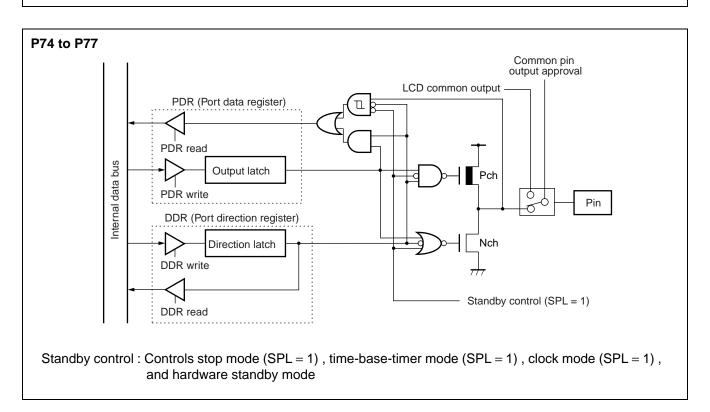

| 50 to 62                                        | P74 to P77                  |         | General-purpose I/O ports<br>Only available when the LCD controller/driver control register is set to the<br>ports.                                         |

| 59 to 62                                        | COM0 to<br>COM3             | L       | Common pins for the LCD controller/driver<br>Only available when the LCD controller/driver control register is set to the<br>common outputs.                |

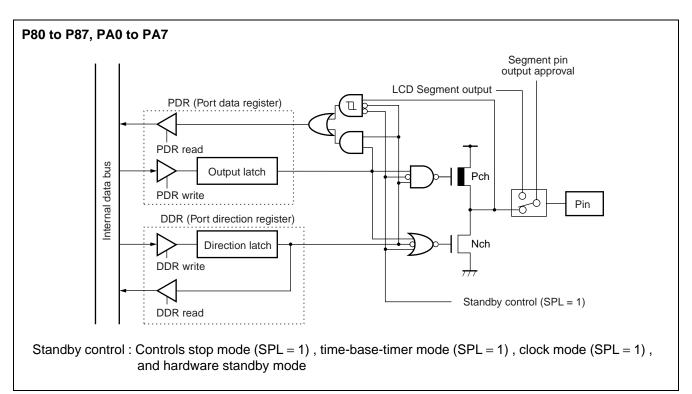

| 64 to 71                                        | P80 to P87                  |         | General-purpose I/O ports<br>Only available when the LCD controller/driver control register is set to the<br>ports.                                         |

| 64 10 7 1                                       | SEG16 to<br>SEG23           | L       | LCD segment output pins for the LCD controller/driver<br>Only available when the LCD controller/driver control register is set to the<br>segment outputs.   |

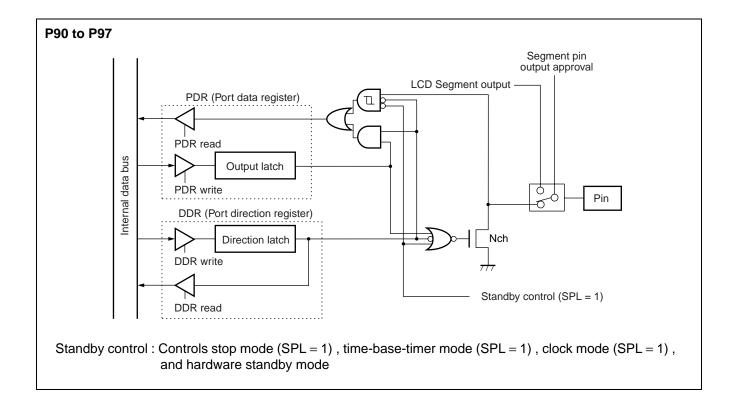

| 72,                                             | P90,<br>P91 to P97          | М       | General-purpose I/O ports (Support up to $I_{OL} = 10$ mA)<br>Only available when the LCD controller/driver control register is set to the<br>ports.        |

| 75 to 81                                        | SEG24,<br>SEG25 to<br>SEG31 | IVI     | LCD segment output pins for the LCD controller/driver<br>Only available when the LCD controller/driver control register is set to the<br>segment outputs.   |

| 17 to 24                                        | SEG0 to<br>SEG7             | F       | LCD segment 00 to 07 pins for the LCD controller/driver                                                                                                     |

| 25 to 32                                        | PA0 to PA7                  | L       | General-purpose I/O ports<br>Only available when the LCD controller/driver control register is set up to<br>the ports.                                      |

| 2010 02                                         | SEG8 to<br>SEG15            |         | LCD segment 08 to 15 pins for the LCD controller/driver<br>Only available when the LCD controller/driver control register is set to the<br>segment outputs. |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

(Continued)

| Pin No.                                         | Circuit  |                 |                                                                                                                                                                                        |  |

|-------------------------------------------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP-120 <sup>*1</sup><br>QFP-120 <sup>*2</sup> | Pin Name | Туре            | Function                                                                                                                                                                               |  |

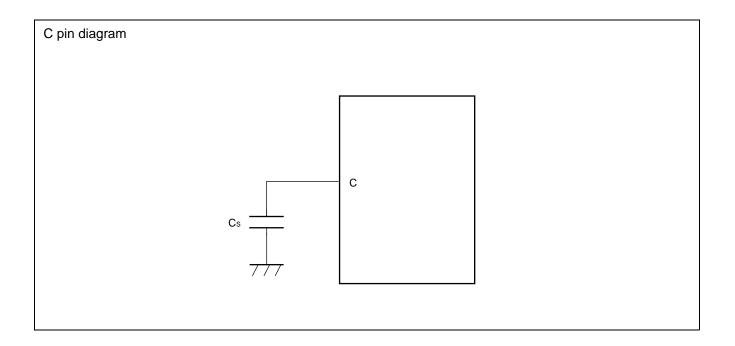

| 34                                              | С        | G               | Capacitor connection pin for stabilizing power supply Connect an external ceramic capacitor of approximately 0.1 $\mu$ F. If operating at 3.3 V or lower, connect to V <sub>cc</sub> . |  |

| 82 to 85                                        | V0 to V3 | Ν               | Power supply input pins for the LCD controller/driver                                                                                                                                  |  |

| 8, 54, 94                                       | Vcc      | Power<br>supply | Power supply input pins for the digital circuit                                                                                                                                        |  |

| 33, 63, 91, 119                                 | Vss      | Power<br>supply | GND level power supply input pins for the digital circuit                                                                                                                              |  |

| 42                                              | AVcc     | Н               | Power supply input for the analog circuit Ensure that a voltage greater than $AV_{CC}$ is applied to $V_{CC}$ before turning the analog power supply on or off.                        |  |

| 43                                              | AVRH     | J               | "H" reference voltage for the A/D converter<br>Ensure that a voltage greater than AVRH is applied to AVcc before turning<br>the power supply to this pin on or off.                    |  |

| 44                                              | AVRL     | Н               | "L" reference voltage for the A/D converter                                                                                                                                            |  |

| 45                                              | AVss     | Н               | GND level power supply input pin for the analog circuit                                                                                                                                |  |

| 38                                              | DVcc     | Н               | "H" reference voltage for the D/A converter<br>Ensure that this voltage does not exceed Vcc.                                                                                           |  |

| 39                                              | DVss     | Н               | "L" reference voltage for the D/A converter<br>Apply the same voltage level as Vss.                                                                                                    |  |

\*1 : FPT-120P-M05

\*2 : FPT-120P-M13

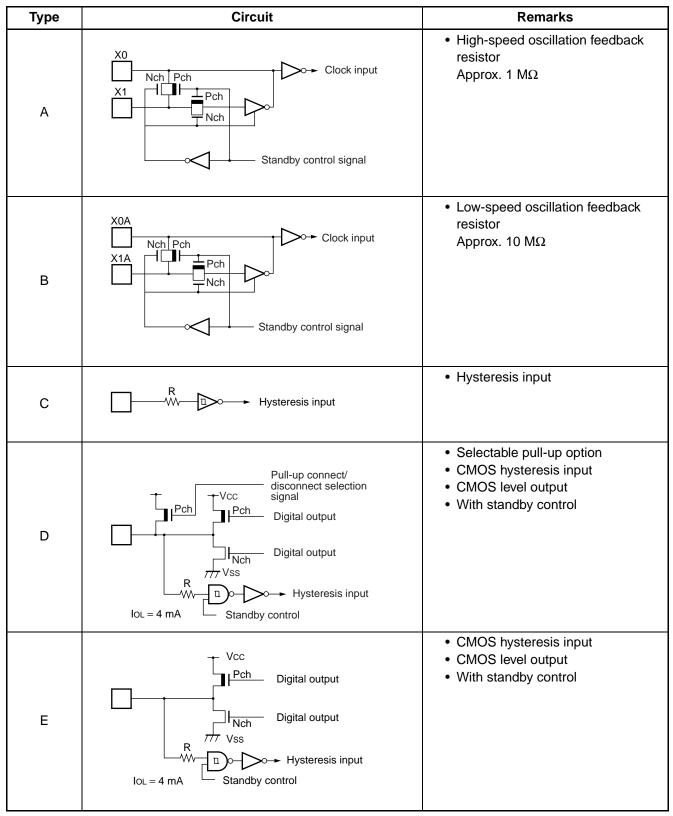

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                                                      | Remarks                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | Vcc<br>R<br>Nch<br>777 Vss                                                                                   | Segment output pins                                                                                                                                                                                                                             |

| G    | Vcc<br>Pch<br>Nch<br>777 Vss                                                                                 | Capacitor connection pin<br>(This is an N.C. pin on the<br>MB90522A and MB90523A.)                                                                                                                                                              |

| н    | AVP                                                                                                          | Analog power supply input<br>protection circuit                                                                                                                                                                                                 |

| I    | Vcc<br>Pch Digital output<br>Nch Digital output<br>777 Vss<br>IOL = 4 mA<br>Standby control<br>Analog output | <ul> <li>CMOS hysteresis input</li> <li>CMOS level output<br/>(CMOS output is not available when<br/>analog output is operating.)</li> <li>Also used as analog output<br/>(Analog output has priority)</li> <li>With standby control</li> </ul> |

| J    | Vcc<br>Pch<br>Pch<br>ANE<br>AVP<br>AVP<br>Nch<br>Vss                                                         | A/D converter ref+ power supply<br>input pin<br>(Incorporates power supply<br>protection circuit.)  (Continued)                                                                                                                                 |

| Туре | Circuit                                                                                                                                        | Remarks                                                                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| к    | Vcc<br>Pch Digital output<br>Nch Digital output<br>777 Vss<br>IoL = 4 mA<br>Standby control<br>Analog input                                    | <ul> <li>CMOS hysteresis input</li> <li>CMOS level output</li> <li>Also used as analog input.</li> <li>With standby control</li> </ul>                                                                          |

| L    | Vcc<br>Pch Digital output<br>Nch Digital output<br>777 Vss<br>IoL = 4 mA $Hysteresis input$<br>Standby control<br>Segment output/common output | <ul> <li>CMOS hysteresis input</li> <li>CMOS level output</li> <li>Also used as segment output pin.</li> <li>With standby control<br/>(only available when segment<br/>output is not operating.)</li> </ul>     |

| М    | IoL = 10  mA                                                                                                                                   | <ul> <li>CMOS hysteresis input</li> <li>N-ch open-drain output</li> <li>Also used as segment output pin.</li> <li>With standby control<br/>(only available when segment<br/>output is not operaing.)</li> </ul> |

| Ν    | IOL = 10  mA                                                                                                                                   | Reference voltage pin for LCD controller                                                                                                                                                                        |

### HANDLING DEVICES

Take note of the following points when handling devices :

- Do not exceed maximum rated voltage (to prevent latch-up)

- Supply voltage stability

- Power-on precautions

- · Power supply pins

- Crystal oscillator circuit

- Notes on using an external clock

- · Precautions when not using sub-clock mode

- Treatment of unused pins

- Treatment of N.C. pins

- Treatment of pins when A/D converter is not used

- Sequence for connecting and disconnecting the A/D converter power supply and analog input pins

- · Shared use of general-purpose I/O ports and LCD controller/driver SEG/COM pins

- Conditions when output from ports 0 and 1 is undefined

- Initialization

- · Notes on using the DIV A, Ri and DIVW A, RWi instructions

- Notes on using REALOS

#### **Device Handling Precautions**

#### • Do not exceed maximum rated voltage (to prevent latch-up)

Latch-up occurs in CMOS ICs if a voltage greater than  $V_{cc}$  or less than  $V_{ss}$  is applied to an input or output pin (other than a high or medium withstand voltage pin) or if the voltage applied between  $V_{cc}$  and  $V_{ss}$  exceeds the rating. If latch-up occurs, the power supply current increases rapidly resulting in thermal damage to circuit elements. Therefore, ensure that maximum ratings are not exceeded in circuit operation.

Similarly, when turning the analog power supply on or off, ensure the analog power supply voltages (AVcc, AVRH, DVcc) and analog input voltages do not exceed the digital voltage (Vcc).

Also ensure that the voltages applied to the LCD power supply pins (V3 to V0) do not exceed the power supply voltage ( $V_{CC}$ ).

#### Supply voltage stability

Rapid changes in supply voltage may cause the device to misoperate, even if the voltage remains within the allowed operating range. Accordingly, ensure that the Vcc supply is stable.

The standard for power supply voltage stability is a peak-to-peak V<sub>CC</sub> ripple voltage at the mains supply frequency (50 to 60 Hz) of 10% or less of V<sub>CC</sub> and a transient voltage change rate of 0.1 V/ms or less when turning the power supply on or off.

#### Power-on precautions

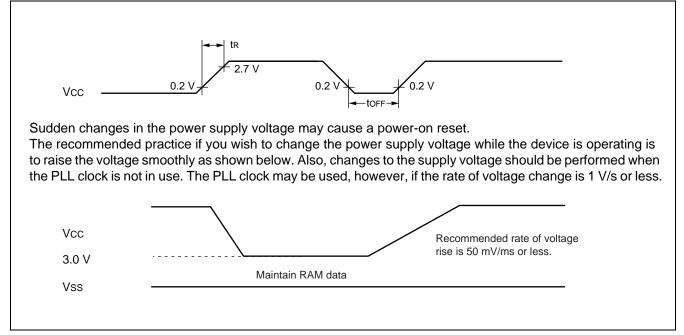

To prevent misoperation of the internal regulator circuit at power-on, ensure that the power supply rising time (0.2 V to 2.7 V) is at least 50  $\mu$ s.

#### Power supply pins

When multiple V<sub>cc</sub> and V<sub>ss</sub> pins are provided, connect all V<sub>cc</sub> and V<sub>ss</sub> pins to power supply or ground externally. Although pins at the same potential are connected together in the internal device design so as to prevent misoperation such as latch-up, connecting all V<sub>cc</sub> and V<sub>ss</sub> pins appropriately minimizes unwanted radiation, prevents misoperation of strobe signals due to increases in the ground level, and keeps the overall output current rating.

Also, ensure that the impedance of the Vcc and Vss connections to the power supply are as low as possible.

Connection of a bypass capacitor of approximately 0.1  $\mu$ F between V<sub>cc</sub> and V<sub>ss</sub> is recommended to prevent power supply noise. Connect the capacitor close to the V<sub>cc</sub> and V<sub>ss</sub> pins.

#### Crystal oscillator circuit

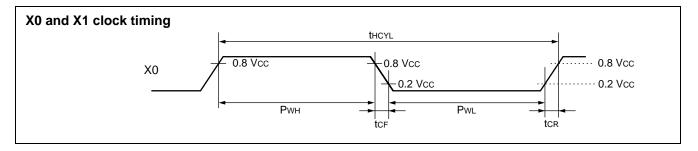

Noise on the X0 and X1 pins can be a cause of device misoperation. Place the X0 and X1 pins, crystal oscillator (or ceramic oscillator), and bypass capacitor to ground as close together as possible. Also, design the circuit board so that the X0 and X1 pin wiring does not cross other wiring.

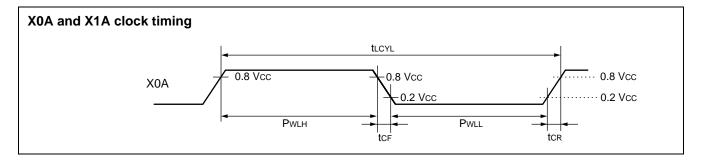

Surrounding the X0/X1 and X0A/X1A pins with ground in the printed circuit board design is recommended to ensure stable operation.

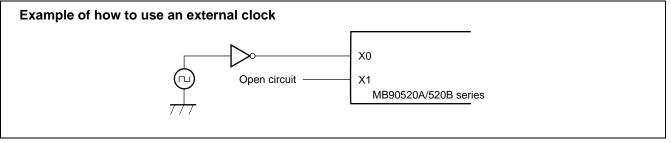

#### Notes on using an external clock

When using an external clock, drive the X0 pin only and leave the X1 pin open. The figure below shows an example of how to use an external clock.

#### · Precautions when not using sub-clock mode

Connect an oscillator to X0A and X1A, even if not using sub-clock mode.

#### • Treatment of unused pins

Leaving unused input pins unconnected can cause misoperation or permanent damage to the device due to latchup. Always pull-up or pull-down unused pins using a 2 k $\Omega$  or larger resistor.

If some I/O pins are unused, either set as outputs and leave open circuit or set as inputs and treat in the same way as input pins.

#### • Treatment of N.C. pins

Always leave N.C. (non connect) pins open circuit.

#### • Treatment of pins when A/D converter not used

When not using the A/D converter and D/A converter, always connect  $AV_{CC} = DV_{CC} = AVRH = V_{CC}$  and  $AV_{SS} = AVRL = V_{SS}$ .

#### • Sequence for connecting and disconnecting the A/D converter power supply and analog input pins

Do not apply voltage to the A/D and D/A converter power supply (AVcc, AVRH, AVRL, DVcc, DVss) or analog inputs (AN0 to AN7) until the digital power supply (Vcc) is turned on.

When turning the device off, turn off the digital power supply after disconnecting the A/D converter power supply and analog inputs. When turning the power on or off, ensure that AVRH and DVcc do not exceed AVcc (turning the analog and digital power supplies on and off simultaneously is OK).

#### Shared use of general-purpose I/O ports and LCD controller/driver SEG/COM pins

The SEG08 to SEG31 and COM0 to COM3 pins are shared with general-purpose I/O ports. The electrical ratings for SEG08 to SEG23 and COM0 to COM3 are the same as for CMOS outputs and the electrical ratings for SEG24 to SEG31 are the same as for N-ch open-drain ports.

#### • Conditions when output from ports 0 and 1 is undefined

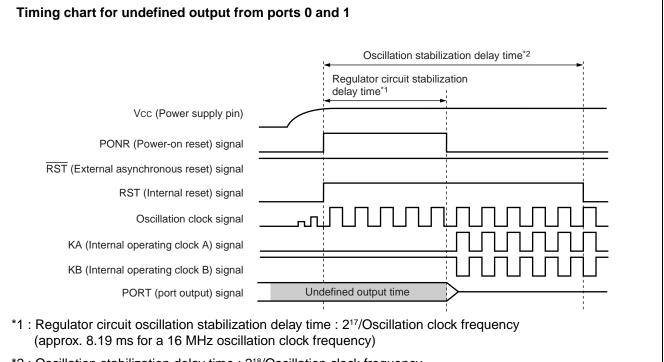

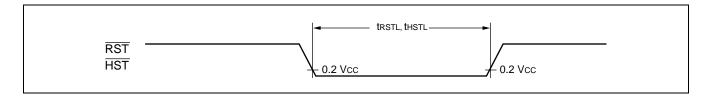

After turning on the power supply, the outputs from ports 0 and 1 are undefined during the oscillation stabilization delay time controlled by the regulator circuit (during the power-on reset). The figure below shows the timing.

Note that this undefined output period does not occur on products without an internal regulator circuit as these products do not have an oscillation stabilization delay time.

\*2 : Oscillation stabilization delay time : 2<sup>18</sup>/Oscillation clock frequency (approx. 16.38 ms for a 16 MHz oscillation clock frequency)

Note : See the "■ PRODUCT LINEUP" section for details of which MB90520A/520B series products have an internal regulator circuit.

#### Initialization

The device contains internal registers that are only initialized by a power-on reset. To initialize these registers, restart the power supply.

#### • Notes on using the DIV A, Ri and DIVW A, RWi instructions

Set the corresponding bank registers (DTB, ADB, USB, SSB) to "00<sub>H</sub>" when using the signed division instructions "DIV A, Ri" and "DIVW A, RWi".

If the corresponding bank registers (DTB, ADB, USB, SSB) are set to other than "00<sub>H</sub>", the remainder value produced by the instruction is not stored in the instruction operand register.

#### Notes on using REALOS

The extended intelligent I/O service (El<sup>2</sup>OS) cannot be used when using REALOS.

#### Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

#### • BLOCK DIAGRAM

- \*1 : The clock control circuit includes the watchdog timer and timebase timer low power consumption control circuits.

- \*2 : Incorporates a pull-up register setting register. CMOS level input and output.

- \*3 : As this port shares pins with the LCD output, the port uses N-ch open-drain circuits.

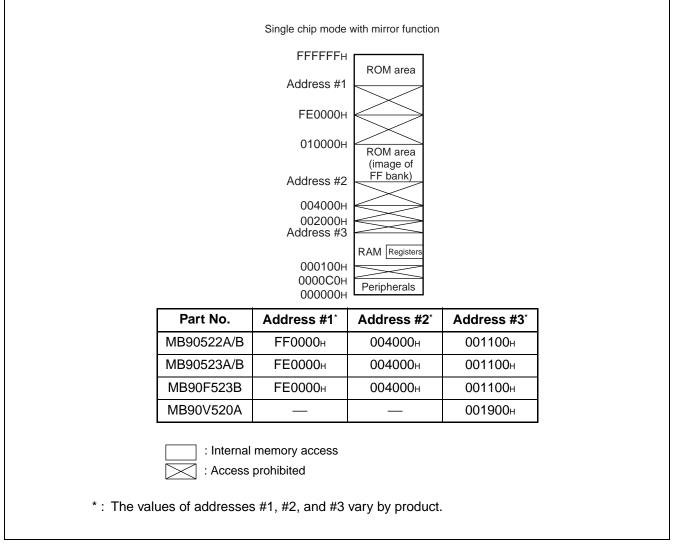

#### MEMORY MAP

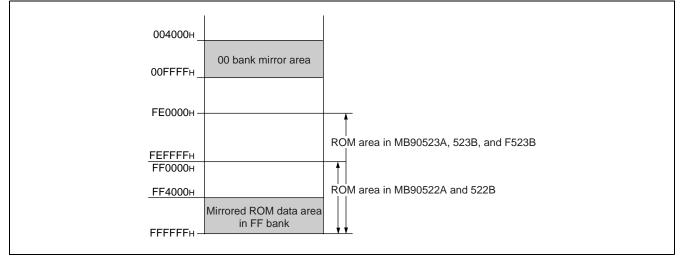

Note : The upper part of 00 bank contains a mirror of the ROM data in FF bank. This is called the mirror ROM function and enables use of the C compiler's small memory model. As the lower 16 bits of the FF bank and 00 bank addresses are the same, tables located in ROM can be referenced without needing to declare far pointers.

For example, accessing  $00C000_{H}$  actually accesses the contents of ROM at FFC000<sub>H</sub>. Note that, as the FF bank ROM area exceeds 48 KBytes, the entire ROM image cannot be mirrored in 00 bank. Accordingly, as ROM data from FF4000<sub>H</sub> to FFFFFF<sub>H</sub> is mirrored in 004000<sub>H</sub> to 00FFFF<sub>H</sub>, always locate ROM data tables in the range FF4000<sub>H</sub> to FFFFFF<sub>H</sub>.

### ■ I/O MAP

| Address         | Abbreviated<br>Register<br>Name | Register Name                                                      | Peripheral Name       | Initial Value              |

|-----------------|---------------------------------|--------------------------------------------------------------------|-----------------------|----------------------------|